# First Order Current-Mode Universal Building Block

Lukas Burian, Pravoslav Martinek

Department of Circuit Theory, Faculty of Electrical Engineering, Czech Technical University in Prague, Technicka 2, 166 27 Prague, Czech Republic

E-mail: burial2@fel.cvut.cz, martinek@fel.cvut.cz

#### Abstract:

This paper deals with design of second generation current conveyor and transconductance amplifier for the 1<sup>st</sup> order current-mode universal building block. The universal building block is able to provide transfer of high-pass and low-pass in one circuit. With the multi-output CCII and OTA, it is possible to create various transfer function.

The current conveyor is designed to have very low input impedance and very high output impedance. For this purpose auxiliary feedback was used for port X and original arrangement of output current mirrors decreasing supply power. Transconductance amplifier is based on simple differential pair in the input stage.

# INTRODUCTION

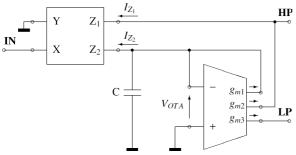

In [7] we have early presented an idea of the 1st-order universal current-mode building block suitable for a low-pass, high-pass and all-pass filter realizations. The purpose of this paper is to show a CMOS implementation of such a block and to present the real properties of the designed circuit. The general block diagram of the universal block is shown in Fig. 1. As evident, a current follower (CF) and a transconductance amplifier (OTA) are the basic subblocks.

Fig. 1: First order current-mode building block [7]

The final solution is based on a Double-Output Current Conveyor (DOCCII+) serving as a current follower and a multiple-output transconductance amplifier. The specified block diagram is introduced in Fig. 2. As can be easily derived, the main transfers

Fig. 2: First order current-mode building block – final form

corresponding to the low-pass and high-pass filters are expressed by Eqs. (1) and (2) in the form

$$H(s)_{LP} = \frac{\beta_2 g_{m3}}{sC + g_{m1}};$$

(1)

$$H(s)_{HP} = \frac{\beta_2 g_{m2}}{sC + g_{m1}} - \beta_1.$$

(2)

Note that the setting of  $\beta_1 = \beta_2 = \beta$  and  $g_{m1} = g_{m2} = g_m$  leads to the simplification of the previous equations (1), (2) to the form (3):

$$H(s)_{LP} = \frac{\beta}{1 + s\tau}; H(s)_{HP} = \beta \frac{s\tau}{1 - s\tau}, \quad (3)$$

where  $\tau = \frac{C}{g_{m}}$ .

# **BUILDING BLOCK DESIGN**

Now, let us an attention to the sub-blocks design. The additional requirements to their properties are as follows:

- 1. The positive second-generation current conveyor with double output (DOCCII+) has port Y grounded. Port X creates an input port of the block. That's why the input impedance needs to be as low possible.

- 2. The transconductance  $g_m$  of the transconductance amplifier (OTA) is given by possible values of integrated capacitor and frequencies in the range of tenths of MHz. According to this,  $g_m$  should be at least  $100\mu S$  and OTA needs also a triple output with equal characteristics.

3. Current mirrors are the critical parts of both the partial blocks. In accordance to Ref. [9], the cascode current mirrors with external biasing were used. This provides high output impedance, high bandwidth and reasonable input voltage and minimum output voltage lower than common cascode mirror.

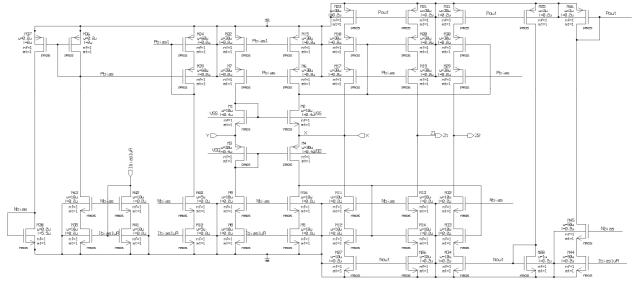

$I_{OFFSET}$  = - 66nA@ $I_{IN}$ =0 and input current range  $\pm 100 \mu A$ . Power consumption with zero input signal is 1,4mW (350 $\mu A$  at 4V). Input impedance of port X and output impedances on both port Z1 and Z2 are in Table 1. Gain bandwidth given by 3dB decrease of current transfer is 512 MHz.

Fig. 3: Double Output Current Conveyor DOCCII+

## **Current Conveyor (CC)**

The input stage of DOCCII+ is translinear loop in class AB. To create current input with low input impedance, the modification of translinear loop [3] was used. The input current now flows mainly through the added current mirrors and not through the translinear loop. This is why the operating point of the translinear loop does not alter with input current and provides good voltage transfer from the port Y to X. The feedback decreases input impedance on the current input X according to feedback loop gain.

This modification leads to very high current (1mA) flow through output mirrors and make proper function of them impossible because transistors runs out from saturation. It was necessary to set the current lower, but preserve low input impedance on port X.

The additional resistors were added in series with current mirrors as is commonly used for increasing output impedance. This arrangement decreases voltage on gates of transistors in output mirrors and does not change the signal path. The resistors are finally replaced by other transistors in connection known as active load. The output impedance is now greater and power consumption is reasonable. Output voltage range is quite decreased by voltage on two extra transistors but it is acceptable.

The double output of DOCCII+ is done by duplication of the output mirrors. Both outputs have equal characteristics and current transfer  $\beta$  can be easily changed for each output independently.

The final circuit diagram is shown in Fig. 3. Designed CC has current transfer  $\beta = 0.997$  with offset

Tab. 1. Input and output impedances of designed DOCCII+ and TOOTA

| Frequency | DOCCII+       |                       | TOOTA                   |                         |

|-----------|---------------|-----------------------|-------------------------|-------------------------|

|           | input         | output                | input                   | output                  |

|           | impedance     |                       | impedance               |                         |

| 0,1 MHz   | $47~\Omega$   | $52~\mathrm{M}\Omega$ | 99 M $\Omega$           | 147 $M\Omega$           |

| 1 MHz     | $50 \Omega$   | $52~\mathrm{M}\Omega$ | $24~\mathrm{M}\Omega$   | $152  \mathrm{M}\Omega$ |

| 10 MHz    | $172 \Omega$  | $50\mathrm{M}\Omega$  | $2.5~\mathrm{M}\Omega$  | 161 M $\Omega$          |

| 100 MHz   | $2015 \Omega$ | $40~\mathrm{M}\Omega$ | $0.25~\mathrm{M}\Omega$ | 161 M $\Omega$          |

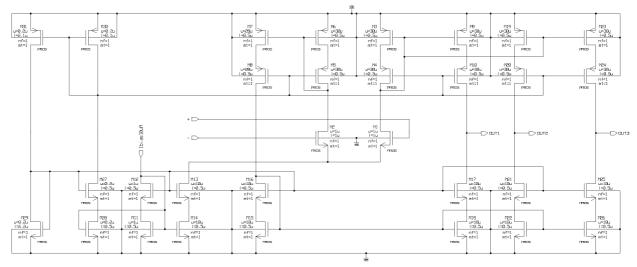

### **Transconductance amplifier (OTA)**

Transconductance amplifier is designed to have transconductance  $g_m$  at about  $100\mu S$  and triple output with identical characteristics with ability to change  $g_m$  independently. The low  $g_m$  allow to use quite high tail current ( $I_{SS}=100\mu A)$  of differential pair to achieve linearity better than 1% for differential input voltages in range about  $\pm 160mV.$

Final transconductance of the TOOTA is  $g_{\rm m}=192~\mu S$  with bandwidth 184 MHz. Input and output impedances are summarized in Table 1. Output impedance is simulated with differential input voltage  $V_{\rm IN}=100mV$  and output voltage 0 and 100mV.

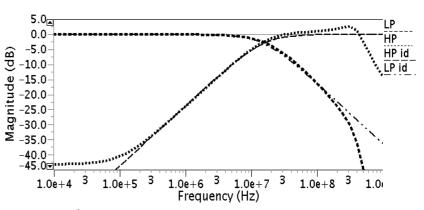

# The designed current-mode building block properties

The designed sub-blocks DOCCII+ and TOOTA were used for the 1<sup>st</sup> order current-mode building block simulation in accordance to the Fig. 2.

For C = 2pF,  $\beta$  = 0,997 and  $g_m$  = 192  $\mu S$  we get the LP pole output 15 MHz. Figure 5 shows a comparison of block assembled from the ideal blocks with provided parameters (curves "HP id" and "LP id") to the designed blocks (curves "HP" and "LP"). The differences in critical points are just a few tenths of dB. The lowest current transfer of output HP is -43dB, in the pass-band is about +1dB. Current transfer of output LP is -0,1dB in the pass-band.

### CC possible improvement

The presented circuit of DOCCII+ is a subject of further research and is being redesigned to allow lower power supply voltage and to migrate to  $1\mu m$  technology. For all current mirrors in circuit were used regulated cascode current mirrors [11]. Operation points of transistors were set to inversion coefficient IC between 0.1 and 1. This brings us high accuracy of current transfer  $\beta = 0.998$  and extremely high output impedance. Power

consumption decreases under  $50\mu W$  at power supply voltage 1.2V for zero input signal. Input currents range is now  $\pm 5\mu A$ . Gain bandwidth falls down to 25 MHz.

# CONCLUSION

Presented circuit is designed and simulated in CMOS technology. The characteristics show that it is possible to use the building block in current mode circuits for frequencies up to 180MHz. The main contribution of this paper is the design of current conveyor. The improvement of traditional circuit decreases input impedance and power consumption and increases output impedance together with wide bandwidth with maximum frequency at 512 MHz.

Fig. 4: Double Output Current Conveyor DOCCII+

## ACKNOWLEDGMENT

The authors would like to thank the Czech Grant Agency (GA ČR) for supporting this work under Grant 102/07/1186 and to the Czech Technical University in Prague under the research program "Research in the Area of the Prospective Information and Navigation Technologies" No. MSM6840770014.

Fig. 5: The simulated frequency responses

### REFERENCES

- [1] Gray P.R., Hurst P.J., Lewis S.H., Meyer R.G.: Analysis and design of analog integrated circuits, Fourth Edition. John Wiley & Sons, New York, 2001. ISBN 0-471-32168-8.

- [2] Tomazou C., Lidgey F.J., Haigh D.G.: Analog IC Design: the current-mode approach. Peter Peregnius Ltd., Herts, 1990. ISBN 0-86341-297-1.

- [3] Salem S.B. and co.: A 2.5V 0,35µm CMOS Current Conveyor and High Frequency High-Q Band-Pass Filter. http://www.tsi.enst.fr/publications/telecomparis/inproceedings-2004-5044.pdf

- [4] Hospodka J.: Základní elektronické prvky a jejich modely. (september 2008). http://www.hippo.feld.cvut.cz/vyuka/elo/

- [5] Fujimori I.: Low voltage self cascode current mirror. US Patent 5966005. http://www.google.com/patents

- [6] Ferri G., Guerrini C. N.: Low-Voltage Low-Power CMOS Current Conveyors. Kluwer Academic Publishers, Boston, 2003. ISBN 1-4020-7486-7.

- [7] Martinek P.: 1<sup>st</sup>-order current-mode building blocks. Moderní směry výuky elektrotechniky a elektroniky. Brno: Univerzita obrany, Fakulta vojenských technologií, 2005, vol. 1, p. 147-150. ISBN 80-7231-011-9. http://www.vabo.cz/stranky/STO9/sbornik/clank y/Pravoslav\_Martinek.pdf

- [8] Valenta M.: Current-Mode Building block design. diploma thesis, Department of Circuit Theory, CTU FEE, Prague, 2008.

- [9] Fiedler S.A.: High-Swing Cascode Current Mirror. US Patent 5680038. http://www.google.com/patents

- [10] Eldbib I., Musil V.: Self-Cascode Current Controlled CCII based-Tunable. Kluwer Academic Publishers, Boston, 2003. ISBN 1-4020-7486-7.

- [11] Allen P.E., Holberg D.R.: CMOS Analog Circuit Design. Oxford University Press, New York, 2002. ISBN 0-19-511644-5.

- [12] Binkley D.M.: Tradeoffs and Optimization in Analog CMOS Design, John Wiley and Sons Ltd., June 2008, ISBN 978-0-470-03136-0.