# Deterministic Wave and Random Symbol Analogue Phase Synchronizers

António D. Reis<sup>1,2</sup>, José F. Rocha<sup>1</sup>, Atilio S. Gameiro<sup>1</sup>, José P. Carvalho<sup>2</sup>

<sup>1</sup>Dep. de Electrónica e Telecomunicações / Instituto de Telecomunicações, Universidade de Aveiro, 3810 Aveiro, Portugal

<sup>2</sup>Dep. de Fisica / U. D. Remota, Universidade da Beira Interior Covilhã, 6200 Covilhã, Portugal E-mail: adreis@ubi.pt, frocha@det.ua.pt, amg@det.ua.pt.pt, pacheco@ubi.pt

#### **Abstract**:

In this work, we present two synchronizer groups: the Deterministic Wave Analogue Phase Synchronizer and the Random Symbol Analogue Phase Synchronizer.

In the first group, the VCO (Voltage Controlled Oscillator) synchronizes with the expected phase of the input deterministic wave and in the second group, the VCO synchronizes with the unexpected phase of the input random symbols.

In each group, we present two topologies which are the analog (full-analogue) and the hybrid (semi-analogue). Our main objective is to study the two groups of synchronizers with its two topologies and to observe its jitter behavior as function of the noise.

Key words: Synchronism in Digital Communications

## INTRODUCTION

This work deal with two synchronizer groups, which are the deterministic wave analogue phase synchronizers and the random symbol analogue phase synchronizers.

In the first group, its VCO synchronizes with an input regular wave and in the second group the VCO synchronizes with an input random symbols.

Each group has two analogue topologies, being one analog (full-analogue) and the other hybrid (semi-analogue).

In the analog case, the input signal and VCO output are both analog (full-analogue). In the hybrid, the input signal is digital and the VCO output is analog (semi-analogue).

Our interest is to study the two groups, each one with two types and observe its behavior in the presence of the noise.

Basically, the synchronizer consists on a VCO that follows the input signal. The input signal can be a regular deterministic wave or an irregular random symbols.

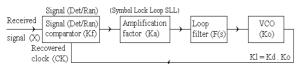

Following figure (Fig.1) shows the block diagram of a general synchronizer.

Fig.1 General deterministic or random synchronizer

The F(s) is the loop filter, Ko is the VCO gain, Kf is the signal comparator gain and Ka is the control parameter of the loop gain, that acts in the locus root, providing the desired characteristics.

Next, we present the two groups of synchronizers, firstly the deterministic wave analogue phase synchronizers and after the random symbol analogue phase synchronizers. Each group has two types, namely the analog and the hybrid.

After, in each group, we test its two synchronizer types with a signal corrupted by noise.

Then, we present the results and we make some comparisons.

Finally, we present some conclusions.

# DETERMINISTIC WAVE PHASE SYNCHRONIZERS

In this group, deterministic wave analogue phase synchronizers, we present two types: the analog and the hybrid [1, 2].

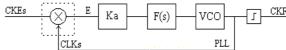

Following figure (Fig.2) shows the analog type, which is based on an analog ideal switch (multiplier).

Fig.2 Analog deterministic wave phase synchronizer

The signal (deterministic) phase comparator is analog type since it is based on an analog ideal switch. So it provides the analog deterministic wave phase synchronizer.

The ideal switch is an analog component without memory, then the respective wave synchronizer is a device without intern memory.

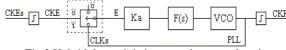

Following figure (Fig.3) shows the hybrid type, which is based on an hybrid real switch.

Fig.3 Hybrid deterministic wave phase synchronizer

The signal (deterministic) phase comparator is hybrid type since it is based on an hybrid real switch. So it provides the hybrid deterministic wave phase synchronizer.

The real switch is an hybrid component without memory, then the respective wave synchronizer is a device without intern memory.

# RANDOM SYMBOL PHASE SYNCHRONIZERS

In this group, random symbol analogue phase synchronizers, we present two types: the analog and the hybrid [3, 4].

Following figure (Fig.4) shows the analog type which is based on an analog ideal switch (multiplier).

Fig.4 Analog random symbol phase synchronizer

The signal (random) phase comparator is analog type since it is based on an ideal analog switch. So it provides the analog random symbol phase synchronizer.

The ideal switch is an analog component without memory, then the respective symbol synchronizer is a device without intern memory.

Following figure (Fig.5) shows the hybrid type which is based on an hybrid real switch.

Fig.5 Hybrid random symbol phase synchronizer

The signal (random) phase comparator is hybrid type since it is based on an real hybrid switch. So it provides the hybrid random symbol phase synchronizer.

The real switch is an hybrid component without memory, then the respective symbol synchronizer is a device without intern memory.

## TESTS, DESIGN AND RESULTS

We will present the tests, the design and the results of the referred synchronizers [5].

### **Tests**

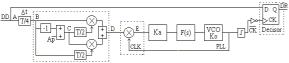

The following figure (Fig.6) shows the setup that was used to test the various synchronizers.

Fig.6 Block diagram of the test setup

The receiver recovered clock with jitter is compared with the emitter original clock without jitter, the difference is the jitter of the received clock.

#### Jitter measurer (Meter)

The jitter measurer (Meter) consists of a RS flip flop, which detects the random variable phase of the recovered clock (CKR), relatively to the fixed phase of the emitter clock (CKE).

This relative random phase variation is the recovered clock jitter (Fig.7).

The other blocks convert this random phase variation into a random amplitude variation, which is the jitter histogram.

Then, the jitter histogram is sampled and processed by an appropriate program, providing the RMS jitter and the peak to peak jitter.

#### Design

To get guaranteed results, it is necessary to dimension all the synchronizers with equal conditions. Then it is necessary to design all the loops with identical linearized transfer functions.

The general loop gain is Kl=Kd.Ko=Ka.Kf.Ko where Kf is the phase comparator gain, Ko is the VCO gain and Ka is the control amplification factor that permits the desired characteristics.

For analysis facilities, we use a normalized transmission rate tx=1baud, what implies also normalized values for the others dependent parameters. So, the normalized clock frequency is fCK=1Hz.

We choose a normalized external noise bandwidth Bn = 5Hz and a normalized loop noise bandwidth Bl = 0.02Hz. Later, we can disnormalize this values to the appropriated transmission rate tx.

Now, we will apply a signal to noise ratio SNR related with the signal amplitude Aef, noise spectral density No and external noise bandwidth Bn, so it is SNR =  $A^2_{ef}/(No.Bn)$ . But No can be related with the noise variance  $\sigma n$  and inverse sampling  $\Delta \tau = 1/Samp$ , then  $No=2\sigma n^2.\Delta \tau$ , so  $SNR=A^2_{ef}/(2\sigma n^2.\Delta \tau.Bn) = 0.5^2/(2\sigma n^2*10^{-3}*5)=25/\sigma n^2$ .

# - 1<sup>st</sup> order loop:

The loop filter F(s)=1 with cutoff frequency 0.5Hz (Bp=0.5 Hz is 25 times bigger than Bl=0.02Hz) eliminates only the high frequency, but maintain the loop characteristics.

The transfer function is

$$H(s) = \frac{G(s)}{1 + G(s)} = \frac{KdKoF(s)}{s + KdKoF(s)} = \frac{KdKo}{s + KdKo}$$

(1)

the loop noise bandwidth is

$$B1 = \frac{KdKo}{4} = Ka \frac{KfKo}{4} = 0.02Hz \tag{2}$$

Then, for the analog synchronizers, the loop bandwidth is

Bl=0.02=(Ka.Kf.Ko)/4 with (Km=1, A=1/2, B=1/2; Ko=2 $\pi$ )

$$(Ka.Km.A.B.Ko)/4 = 0.02 -> Ka = 0.08*2/\pi$$

(3)

For the hybrid synchronizers, the loop bandwidth is Bl=0.02=(Ka.Kf.Ko)/4 with (Km=1, A=1/2, B=0.45; Ko=2 $\pi$ )

$$(Ka.Km.A.B.Ko)/4 = 0.02 -> Ka = 0.08*2.2/\pi$$

(4)

The jitter depends on the RMS signal Aef, on the power spectral density No and on the loop noise bandwidth Bl.

For analog PLL the jitter is  $\sigma \phi^2 = Bl.No/Aef^2 = Bl.2.\sigma n^2.\Delta \tau$ =0.02\*10<sup>-3</sup>\*2\sigma n^2/0.5^2=16\*10<sup>-5</sup>.\sigma n^2

For the others PLLs the jitter formula is more complicated.

# - 2<sup>nd</sup> order loop:

The second order loop is not shown here, but the results are similar to the ones obtained below for the first order loop.

#### Results

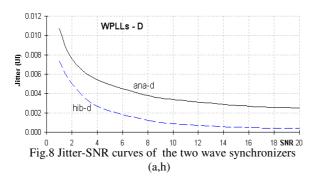

We present the results of the two groups of synchronizers: the deterministic wave and the random symbol. In each group we distinguish two types: the analog and the hybrid.

We will see the jitter UI-RMS (Unit Interval Root Mean Square) as function of the SNR (Signal to noise ratio)

Firstly, we present the jitter-SNR curves of the deterministic wave synchronizer types: the analog (ana-d) and the hybrid (hib-d) (Fig.8).

We verify, that the synchronizer without input limiter (ana) is disadvantageous relatively to the one with input limiter (hib).

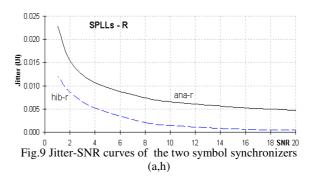

After, we present the jitter-SNR curves of the random symbol synchronizer types: the analog (ana-r) and the hybrid (hib-r) (Fig.9).

We verify that the synchronizer without input limiter (ana) is disadvantageous over the other with input limiter (hib).

## **CONCLUSIONS**

We studied two synchronizer groups, which are the deterministic wave analogue phase synchronizers and the random symbol analogue phase synchronizers. Each group has two types: the analog (ana) and the hybrid (hib).

We verify that for high SNR, the synchronizer without input limiter (ana) is disadvantageous over the other with input limiter (hib). This is comprehensible, because the limiter noise margin ignores low noise spikes.

However, for low SNR the synchronizer without input limiter (ana) tends to be similar with the other with input limiter (hib). This is comprehensible because the limiter provokes random gate commutations.

#### **ACNOWLEDGMENTS**

The authors are grateful to the program FCT (Foundation for sCience and Technology).

## **REFERENCES**

- [1] A. H. Jazwinski, "Filtering for Nonlinear Dynamical Systems" IEEE Automatic Control p.765 October 1966.

- [2] J. C. Imbeaux, "performance of the delay-line multiplier circuit for clock and carrier synchronization", IEEE, J. Sel. Areas in Com., Jan. 1983.

- [3] Werner Rosenkranz, "Phase Locked Loops with limiter phase detectors in the presence of noise", IEEE Transactions on Communications com-30. October 1982.

- [4] Charles R. Hogge, "A Self Correcting Clock Recovery Circuit", Journal of Lightwave Technology, Dec. 1985.

- [5] A. D. Reis, J. F. Rocha, A. S. Gameiro, J. P. Carvalho "A New Technique to Measure the Jitter", III Conference on Telecommunications p.64, F. Foz-PT 23-24 April 2001.