# A Program Procedure for Estimation of the Cross–Coupled Charge Pump Properties

Jan Marek, Jiří Hospodka

Dept. of Circuit Theory

Czech Technical University in Prague - FEE

Technická 2, 166 27 Prague

Czech Republic

{marekj20, hospodka }@fel.cvut.cz

Ondřej Šubrt

<sup>1</sup>ASICentrum, a company of the Swatch group

Novodvorská 994, 142 21 Prague

Czech Republic

ondrej.subrt@asicentrum.cz

<sup>2</sup>Dept. of Circuit Theory

Czech Technical University in Prague - FEE

Technická 2, 166 27 Prague

Czech Republic

subrto@fel.cvut.cz

Abstract—This paper presents the computional algorithm that is used for prediction of the cross-coupled charge pump static and dynamic properties. The calculation method is based on the state-space model of the charge pump for each phase of the clock signal. State equations are drawn from the symbolic relationships of the pump stage as an analog functional block using BSIM equations for long channel MOSFET. The algorithm was programmed in Maple SW and calculated values were compared with transistor-level circuit characteristics. The analysis results show high accuracy of the mentioned method, which allow to reflect many real effects compared to the equivalent digital model description. The algorithm will be used for synthesis procedure together with the application of formulae for optimal design circuit without long-time simulation process.

Keywords - BSIM model; Cross-coupled charge pump; cycle; recurrent expression; simulation; state-space model.

# I. INTRODUCTION

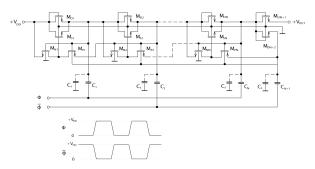

Estimation of the static and dynamic properties of the cross-coupled charge pump (Fig. 1) through the mathematical description is a comprehensive task. Many reasons have been mentioned and demonstrated by the simulation results [5]. Simulations are the usual way of the optimal quasi-analog circuits design. Digital

Fig. 1. Cross-coupled charge pump [5].

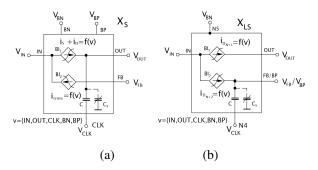

model is not an option due to its low accuracy. However, another aproach has already been outlined in [5]. The previous research has been focused on the description of circuit behavior as an analog block. It allows to include many dominant and undesirable phenomenae (unlike the digital model description), which contribute to reduce pump efficiency - reverse switch current, inverter cross current, body effect, etc. Complete model of each of the stages and last stage (Fig. 2) is detailed in [5]. Behavior of the model was tested in N-stages charge pump by the simulator LT SPICE. The analysis results show the match between the model and the full-transistor SPICE-level simulation in a wide set of the input parameters, as it was evidenced by the characteristics. Subtreshold region of MOSFETs is not expected in normal operation. Current research has

Fig. 2. Subcircuit of the i-pump stage (a) and the last stage (b) [5]

built on the mentioned work. In this paper, the attention will be focused on the program procedure, which allow to estimate the charge pump properties. Firstly, the strategy of the solution through the state description of the system will be explained. The main part deals with principle of the computational algorithm which core is operating with previously derived analytic formulae of the analog blocks ([3], [6]). Algorithm is implemented in Maple SW and achieve results are compared with the full transistor-level properties of the charge pump, which are simulated in professional design environment ELDO. The main benefit of our work is the development of step-by step synthesis procedure by using known relationships without the necessity to use computationally demanding iteration processes.

## II. STATE MODEL OF THE SYSTEM

Generally, the classical control theory and methods that are used to simple input-output description of the plant can not be applied in this case. The reasons are

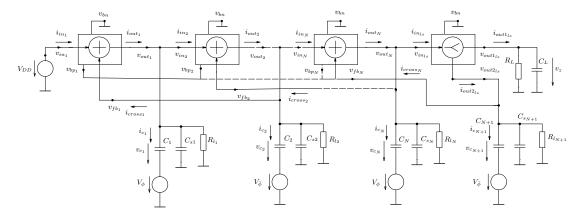

Fig. 3. Block diagram of the N-stage cross-coupled charge pump

based on the non-linear nature of the circuit, which handles discrete values—discontinuity of the inner states in time. But considering the selected time interval defined by the valid logic levels of the clock signals. the circuit may be described as multidimensional continuous nonlinear dynamic system [1]. The internal description leads to the state model of the system [2], block diagram is shown in Fig. 3. Each of the i-pump stage represents block, where the output current  $i_{out_i}$ is given by the sum of the input and cross inverter current,  $i_{out_i} = i_{in_i} + i_{cross_i}$ , and the block of the last stage splits the input current  $i_{in_{ls}}$  into load current and charging current that flows through the last main capacitor  $C_{N+1}$ , then  $i_{in_{ls}}=i_{out1_{ls}}+i_{out2_{ls}}$ . The dynamics of the *state-space* system refers to *state* variables represent by the voltage on the capacitors, that fully describe the system at time  $\langle 0, T_{clk}/2 \rangle$  and its response to any given set of inputs. Assuming the constant clock signal amplitude, the number of state variables with knowledge of those variables at initial time  $t_0 \in \langle 0, T_{clk}/2 \rangle$  is equal to number of main capacitors because the time-varying component of the voltage  $v_{C_i}$  is the only one on the parasitic capacitor. In the other words  $\dot{v}_{C_s} = \dot{v}_{C_i} + \dot{v}_{clk} = \dot{v}_{C_i}$  for valid logic levels. In the standard form, the mathematical description expressed as a set of N+2 (icluding load capacitance  $C_L$ ) coupled first-order ordinary differential equations,

$$\begin{split} \dot{v}_{C_1} = & \frac{1}{C_1 + C_{s_1}} \left[ i_{in_1} - i_{in_2} + i_{cross_1} - \frac{v_{C_1} + V_{clk}}{R_{l_1}} \right] \\ \dot{v}_{C_2} = & \frac{1}{C_2 + C_{s_2}} \left[ i_{in_2} - i_{in_3} + i_{cross_2} - \frac{v_{C_2} + V_{clk}}{R_{l_2}} \right] \\ \vdots \\ \dot{v}_{C_i} = & \frac{1}{C_i + C_{s_i}} \left[ i_{in_i} - i_{in_{i+1}} + i_{cross_i} - \frac{v_{C_i} + V_{clk}}{R_{l_i}} \right] \\ \vdots \\ \dot{v}_{C_N} = & \frac{1}{C_N + C_{s_N}} \left[ i_{in_N} - i_{in_{l_s}} + i_{cross_N} \right] - \\ & - \frac{1}{C_N + C_{s_N}} \frac{v_{C_N} + V_{clk}}{R_{l_N}} \\ \dot{v}_{C_{N+1}} = & \frac{1}{C_N + C_{s_{N+1}}} \left[ i_{out_{2l_s}} - i_{cross_N} \right] - \\ & - \frac{1}{C_N + C_{s_{N+1}}} \frac{v_{C_{N+1}} + V_{clk}}{R_{l_{N+1}}} \\ \dot{v}_z = & \frac{1}{C_L} \left[ i_{out_{1l_s}} - \frac{v_z}{R_L} \right] \end{split}$$

$$(1)$$

where  $\dot{v}=\mathrm{d}v/\mathrm{d}t$ . and each of the functions  $i_{in_i},$   $i_{cross_i},$   $i_{out1_{ls}},$   $i_{out2_{ls}}$  is nonlinear time-varying function of the nodes voltages  $v_{C_i}$ , the system inputs (transistos sizing, power supply, etc.) and time. Resistors  $R_{l_i}$  model leakage current of each of the pump stages and  $R_L$  is main pump load resistance.

## III. THE BASIC PRINCIPLE OF THE ALGORITHM

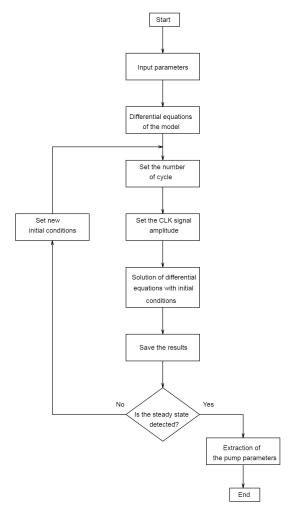

The state model is the core of the analysis algorithm despite its limitations that is mentioned in the previous text. The philosophy of the following approach that allow to estimate static a dynamic charge pump parameters is based on idea of the quasi-analog system. Block structure of the N-stage charge pump (Fig. 3), is described as analog circuit in each phase of the clock signal, while the transition into next phase is characterized by the discrete changes of some input variables (clock signal). The influence of the rising and falling edges of the clock signal is not considered. The new state is dependent on the new input variable but also on the previous state, i.e. recurrent expression. Algorithm diagram is shown in Fig. 4. Reffering to the input parameters (number of stages, clock frequency,...), program procedure automatically generates state equations from (1) with a set of initial conditions and sets amplitude of the clock signal  $V_{\phi}$ ,  $V_{\bar{\phi}}$  from the number of cycle  $k = \{1, 2, ..., n\},\$

$$V_{\phi} = \left\{ \begin{array}{l} 0, & \text{for odd } k \\ V_{DD}, & \text{for even } k \end{array} \right.$$

Zero intial conditions are set in the first cycle that corresponds to the half of the period of the clock signal. It is very important point due to solution convergence. After initialization, the time response characteristics  $v_{C_i}(t)$  and  $v_z(t)$  are computed at time interval

$$t \in \left\langle (k-1) \frac{T_{clk}}{2}, k \frac{T_{clk}}{2} \right\rangle.$$

The end value of the interval is passed as the parameter determining the initial condition to the next cycle. In general form, the inital condition of each of the state

Fig. 4. Charge pump analysis algorithm

variables, labeled  $v_{C_{i_0}}^{(k+1)}, v_{z_0}^{(k+1)},$  in the next cycle is determined as

$$\begin{split} v_{C_{i_0}}^{(k+1)} = & \mathrm{sgn}_{V_{DD}} V_{DD} \cdot \frac{C_s}{C + C_s} + v_{C_i}^{(k)}|_{t = k \cdot T_{clk}/2}, \\ v_{z_0}^{(k+1)} = & v_z^{(k)}|_{t = k \cdot T_{clk}/2}, \\ & \text{for } t \in \left\langle k \frac{T_{clk}}{2}, (k+1) \frac{T_{clk}}{2} \right\rangle, \end{split} \tag{2}$$

where factor  $\mathrm{sgn}_{V_{DD}}$  provides sign of the clock signal amplitude:

$${\rm sgn}_{V_{DD}} = \left\{ \begin{array}{ll} +1, & {\rm for~the~passive~interval~of~CLK} \\ -1, & {\rm for~the~active~interval~of~CLK}, \end{array} \right.$$

after that, the computing process is repeated.

As a result, dynamic behavior of the system within the interval  $t \in \langle 0, k \cdot T_{clk}/2 \rangle$  is obtained by composing partial response characteristics in the appropriate scale.

Computional procedure runs until the the output voltage  $v_z(t)$  achieves the steady state. It means that average value of the output voltage is practically constant over time.

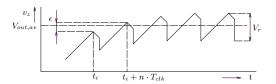

Steady state is simply indicated by comparing two arbitrary values that are temporarily shifted by just one period of the clock signal (see Fig. 5). Consequently,

$$v_z(t_i + T_{clk}) - v_z(t_i) < \epsilon, \tag{3}$$

Fig. 5. Time response characteristics of the pump output voltage

where parameter  $\epsilon$  should be chosen with regard to the numerical calculation accuracy, for example  $\epsilon=1$  mV.

## IV. EXPERIMENTAL PART

The computational algorithm has been programmed in Maple SW according to the structure that is shown in Fig. 3. The influence of the parasitic capacitances  $C_{s_i}$  and shunt resistances  $R_{l_i}$  is taken into account. All the simulations parameters are given in Tab. I.

Under condition (3), the values of the system state variables can be used used to calculate other significant parameters, as power consumption, etc. In addition, procedure checks correct function of the circuit (open loop of feedback is a typical problem for this topology), operation mode of each of the transistors and exceeding the limit parameters  $(V_{DS_{max}}, V_{GS_{max}},$  etc.).

Total number of cycles, labeled n, when the output voltage  $v_z$  starts from the initial value to the final value in steady state is approximately equal to *Rise time*  $T_r$ ,

$$T_r \approx \frac{n}{2} T_{clk}|_{k=n}. (4)$$

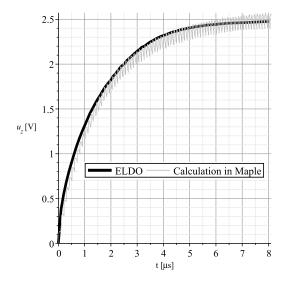

The voltage trend over time  $v_z(t)$  is actually difficult to describe, because it is influenced by many dynamic effects in circuit, as capacitive couplings between stages and charge injection. An example of time response characteristic is shown in the Fig. 6.

Average value  $V_{out,av}$  of the output voltage is estimated as the average value of the minimum and maximum values instead of the numerical integration of  $v_z(t)$  in steady state,

$$V_{out,av} \doteq \frac{v|_{t=k \cdot T_{clk}/2} + v|_{t=(k+1) \cdot T_{clk}/2}}{2},$$

(5)

where k is close to n. The output ripple voltage, labeled  $V_r$ , is given by the difference of the maximal and minimal values,

$$V_r = |v_i - v_{ii}| \text{ for } k \to n, \tag{6}$$

where  $v_i = v|_{t=k \cdot T_{clk}/2}$  and  $v_{ii} = v|_{t=(k+1) \cdot T_{clk}/2}$ .

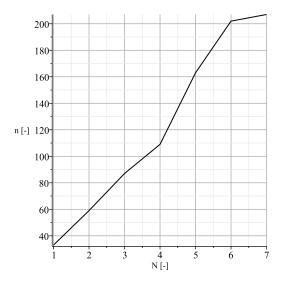

Static and dynamic characteristics were compared with values that have been analyzed by the professional simulator ELDO including SPICE-level models of the components (library MGC Design Kit). Some results are summarized in the following table, including relative average output voltage error  $\epsilon_{V_{out}}$ . Naturally, the computional time increases with the number of circuit nodes, which is associated with the number of pump stages. However, total cycle count is a crucial indicator of computational difficulty. The growth trend, as it is shown in Fig. 7, is limited by the *pump efficiency*.

# TABLE I SIMULATION PARAMETERS

| Parameter                     | Value         |                     |

|-------------------------------|---------------|---------------------|

| Temperature                   | $\vartheta$   | 24 °C               |

| Supply voltage                | $V_{DD}$      | 1V                  |

| Clock frequency               | $f_c$         | 10 MHz              |

| Main capacitance              | $C_i$         | 5 pF                |

| Parasitic capacitance         | $C_{s_i}$     | 0.6 pF              |

| Shunt resistance              | $R_l$         | $10^7 \Omega$       |

| Load ressistance              | $R_L$         | 100 k               |

| Load capacitance              | $C_L$         | 10 pF               |

| Threshold voltage of          | $V_{TH0_N}$   | $0.35{ m V}$        |

| NMOS and PMOS at V=0          | $ V_{TH0_P} $ | $0.33{ m V}$        |

| Channel length of N(P)MOS     | L'L           | $1 \mu \mathrm{m}$  |

| Channel width of the $M_{Si}$ | $W_s$         | $2  \mu \mathrm{m}$ |

| $M_{Pi}$                      | $W_p$         | $20\mu\mathrm{m}$   |

| $M_{Ni}$                      | $W_n$         | $9  \mu \mathrm{m}$ |

| $\mathrm{M}_{Di}$             | $W_d$         | $10\mu\mathrm{m}$   |

#### TABLE II SIMULATION RESULTS

| $\epsilon$ = | = 1 mV | Calculation     | ELDO            |                          |

|--------------|--------|-----------------|-----------------|--------------------------|

| N[-]         | n [-]  | $V_{out,av}[V]$ | $V_{out,av}[V]$ | $\epsilon_{V_{out}}$ [%] |

| 1            | 33     | 1.12            | 1.10            | 1.8                      |

| 2            | 59     | 1.61            | 1.53            | 5.2                      |

| 3            | 87     | 2.02            | 1.93            | 4.6                      |

| 4            | 109    | 2.16            | 2.18            | 0.91                     |

| 5            | 163    | 2.53            | 2.48            | 2                        |

| 6            | 202    | 2.61            | 2.67            | 2.2                      |

| 7            | 207    | 2.57            | 2.47            | 4                        |

Fig. 6. Time response characteristic of the five-stage pump output voltage

## V. CONCLUSION

The analysis algorithm for estimation of static and dynamic parameters of the cross-coupled charge pump was discussed in this paper. The principle is based on the state model analyzing circuit behavior at each phase of the clock signal. The block structure was built from the subcircuits, which include dominant effects via the BSIM model equations. N-stage charge pump structure is described by the N+2 first-order differential equations. Total response characteristics of the output voltage is obtained through the composition of partial responses for each phase of CLK with initial conditions. Algorithm was implemented in Maple

software and calculated parameters were verified by the simulations in the professional design software ELDO, Design Architect-IC v2008.2\_16.4 including the SPICE-level component models in library MGC Design Kit. This method is very accurate because the

Fig. 7. Number of cycles vs number of stages

transistor-level properties can be arbitrarily included in the sub-blocks description, unlike the "digital circuit perception". Furthermore, the knowledge of the state variables allows to estimate many other parameters, for example, power efficiency. On the contrary, the disadvantage is the need to use a recurrent description associated with the total number of cycles. Computational difficulty is derived from the complexity of circuit topology and pumping efficiency (voltage increase) in time, see Fig. 7.

The main benefit is using the algorithm for synthesis procedure. Future work involves Ward's capacitance model into the structure, next step is creation of the design algorithm that is using the existing relationships.

# ACKNOWLEDGMENT

This work has been supported by the grant No. SGS17/183/OHK3/3T/13 of the CTU in Prague.

## REFERENCES

- A. Honkela, Nonlinear switching state-space models. Master's thesis.Helsinki university of technology, 2001.

- [2] D. K. Arrowsmith and C. M. Place, An introduction to dynamical sys tems. Cambridge University Press, Cambridge, 1990.

- [3] J. Marek, J. Hospodka, O. Šubrt, Design rules of the CMOS inverter for voltage converters. International Journal of Engineering and Innovative Technology (IJEIT), Vol.5, Issue 11, 2016. ISSN 2277-3754.

- [4] C. Hu, A. M. Nikenjad, W. Yang, D. Lu, BSIM4.6.4 MOSFET Model: User's Manual. UC Berkeley, 2009.

- [5] J. Marek, J. Hospodka and O. Šubrt, Description of the functional blocks for the cross-coupled charge pump design algorithm, 2017 International Conference on Applied Electronics (AE), Pilsen, Czech Republic, 2017.

- [6] J. Marek, J. Hospodka and O. Šubrt, Guidelines on the switch transistors sizing using the symbolic description for the crosscoupled charge Pump, Radioengineering, Vol. 26, Issue 3, 2017. ISSN 1805-960.